Difference between revisions of "Adapter Board for Rockchip"

Jump to navigation

Jump to search

| Line 14: | Line 14: | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | |||

|1 | |1 | ||

|GND | |GND | ||

| + | |- | ||

|2 | |2 | ||

|MIPI_L0_N | |MIPI_L0_N | ||

| Line 22: | Line 22: | ||

|3 | |3 | ||

|MIPI_L0_P | |MIPI_L0_P | ||

| + | |- | ||

|4 | |4 | ||

|GND | |GND | ||

| Line 27: | Line 28: | ||

|5 | |5 | ||

|MIPI_CK_N | |MIPI_CK_N | ||

| + | |- | ||

|6 | |6 | ||

|MIPI_CK_P | |MIPI_CK_P | ||

| Line 32: | Line 34: | ||

|7 | |7 | ||

|GND | |GND | ||

| + | |- | ||

|8 | |8 | ||

| − | | | + | |MIPI_L1_1 |

|- | |- | ||

|9 | |9 | ||

|MIPI_L1_P | |MIPI_L1_P | ||

| + | |- | ||

|10 | |10 | ||

|GND | |GND | ||

| Line 42: | Line 46: | ||

|11 | |11 | ||

|MIPI_L2_N | |MIPI_L2_N | ||

| + | |- | ||

|12 | |12 | ||

|MIPI_L2_P | |MIPI_L2_P | ||

| Line 47: | Line 52: | ||

|13 | |13 | ||

|GND | |GND | ||

| + | |- | ||

|14 | |14 | ||

|MIPI_L3_N | |MIPI_L3_N | ||

|- | |- | ||

|15 | |15 | ||

| − | | | + | |MIPI_L4_P |

| + | |- | ||

|16 | |16 | ||

|GND | |GND | ||

| Line 57: | Line 64: | ||

|17 | |17 | ||

|MIPI_MCLK0 | |MIPI_MCLK0 | ||

| + | |- | ||

|18 | |18 | ||

|GND | |GND | ||

| Line 62: | Line 70: | ||

|19 | |19 | ||

|GPIOx | |GPIOx | ||

| + | |- | ||

|20 | |20 | ||

|MIPI_RST | |MIPI_RST | ||

|- | |- | ||

|21 | |21 | ||

| − | | | + | |SCL_3.3V |

| + | |- | ||

|22 | |22 | ||

| − | | | + | |SDA_3.3V |

|- | |- | ||

|23 | |23 | ||

|GND | |GND | ||

| + | |- | ||

|24 | |24 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| Line 77: | Line 88: | ||

|25 | |25 | ||

|GND | |GND | ||

| + | |- | ||

|26 | |26 | ||

|VCC5V | |VCC5V | ||

| Line 82: | Line 94: | ||

|27 | |27 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| + | |- | ||

|28 | |28 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| Line 87: | Line 100: | ||

|29 | |29 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| + | |- | ||

|30 | |30 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| Line 94: | Line 108: | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | |||

|1 | |1 | ||

|GND | |GND | ||

| + | |- | ||

|2 | |2 | ||

|MIPI_L0_N | |MIPI_L0_N | ||

| Line 102: | Line 116: | ||

|3 | |3 | ||

|MIPI_L0_P | |MIPI_L0_P | ||

| + | |- | ||

|4 | |4 | ||

|GND | |GND | ||

| Line 107: | Line 122: | ||

|5 | |5 | ||

|MIPI_CK_N | |MIPI_CK_N | ||

| + | |- | ||

|6 | |6 | ||

|MIPI_CK_P | |MIPI_CK_P | ||

| Line 112: | Line 128: | ||

|7 | |7 | ||

|GND | |GND | ||

| + | |- | ||

|8 | |8 | ||

|MIPI_L1_N | |MIPI_L1_N | ||

| Line 117: | Line 134: | ||

|9 | |9 | ||

|MIPI_L1_P | |MIPI_L1_P | ||

| + | |- | ||

|10 | |10 | ||

|GND | |GND | ||

| Line 122: | Line 140: | ||

|11 | |11 | ||

|MIPI_L2_N | |MIPI_L2_N | ||

| + | |- | ||

|12 | |12 | ||

|MIPI_L2_P | |MIPI_L2_P | ||

| Line 127: | Line 146: | ||

|13 | |13 | ||

|GND | |GND | ||

| + | |- | ||

|14 | |14 | ||

|MIPI_L3_N | |MIPI_L3_N | ||

| Line 132: | Line 152: | ||

|15 | |15 | ||

|MIPI_L3_P | |MIPI_L3_P | ||

| + | |- | ||

|16 | |16 | ||

|GND | |GND | ||

| Line 137: | Line 158: | ||

|17 | |17 | ||

|MIPI_MCLK0 | |MIPI_MCLK0 | ||

| + | |- | ||

|18 | |18 | ||

|GND | |GND | ||

| Line 142: | Line 164: | ||

|19 | |19 | ||

|GPIOx | |GPIOx | ||

| + | |- | ||

|20 | |20 | ||

|MIPI_RST | |MIPI_RST | ||

|- | |- | ||

|21 | |21 | ||

| − | | | + | |SDA_3.3V |

| + | |- | ||

|22 | |22 | ||

| − | | | + | |SCL_3.3V |

|- | |- | ||

|23 | |23 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| + | |- | ||

|24 | |24 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| Line 157: | Line 182: | ||

|25 | |25 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| + | |- | ||

|26 | |26 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| Line 162: | Line 188: | ||

|27 | |27 | ||

|RESERVE, Not Connected | |RESERVE, Not Connected | ||

| + | |- | ||

|28 | |28 | ||

|GND | |GND | ||

| Line 167: | Line 194: | ||

|29 | |29 | ||

|GND | |GND | ||

| + | |- | ||

|30 | |30 | ||

|VCC5V | |VCC5V | ||

| Line 174: | Line 202: | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | |||

|1 | |1 | ||

|MIPI_L0_N | |MIPI_L0_N | ||

| + | |- | ||

|2 | |2 | ||

|MIPI_L0_P | |MIPI_L0_P | ||

| Line 182: | Line 210: | ||

|3 | |3 | ||

|GND | |GND | ||

| + | |- | ||

|4 | |4 | ||

|MIPI_L1_N | |MIPI_L1_N | ||

| Line 187: | Line 216: | ||

|5 | |5 | ||

|MIPI_L1_P | |MIPI_L1_P | ||

| + | |- | ||

|6 | |6 | ||

|GND | |GND | ||

| Line 192: | Line 222: | ||

|7 | |7 | ||

|MIPI_CK_N | |MIPI_CK_N | ||

| + | |- | ||

|8 | |8 | ||

|MIPI_CK_P | |MIPI_CK_P | ||

| Line 197: | Line 228: | ||

|9 | |9 | ||

|GND | |GND | ||

| + | |- | ||

|10 | |10 | ||

|MIPI_L2_N | |MIPI_L2_N | ||

| Line 202: | Line 234: | ||

|11 | |11 | ||

|MIPI_L2_P | |MIPI_L2_P | ||

| + | |- | ||

|12 | |12 | ||

|GND | |GND | ||

| Line 207: | Line 240: | ||

|13 | |13 | ||

|MIPI_L3_N | |MIPI_L3_N | ||

| + | |- | ||

|14 | |14 | ||

| − | | | + | |MIPI_L4_P |

|- | |- | ||

|15 | |15 | ||

|GND | |GND | ||

| + | |- | ||

|16 | |16 | ||

|MIPI_MCLK0 | |MIPI_MCLK0 | ||

| Line 217: | Line 252: | ||

|17 | |17 | ||

|GND | |GND | ||

| + | |- | ||

|18 | |18 | ||

|GPIOx | |GPIOx | ||

| Line 222: | Line 258: | ||

|19 | |19 | ||

|MIPI_RST | |MIPI_RST | ||

| + | |- | ||

|20 | |20 | ||

| − | | | + | |SCL_3.3V |

|- | |- | ||

|21 | |21 | ||

| − | | | + | |SDA_3.3V |

| + | |- | ||

|22 | |22 | ||

|MIPI_PWR | |MIPI_PWR | ||

| Line 232: | Line 270: | ||

|23 | |23 | ||

|CIF_PWR | |CIF_PWR | ||

| + | |- | ||

|24 | |24 | ||

|VCC5V | |VCC5V | ||

|} | |} | ||

Revision as of 17:19, 25 July 2019

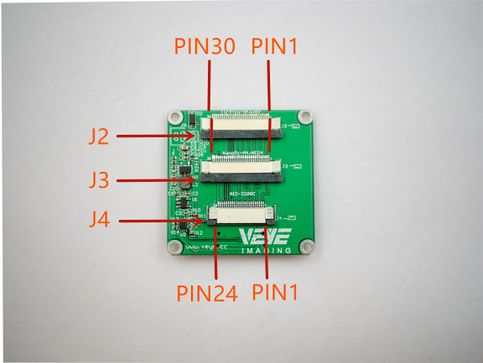

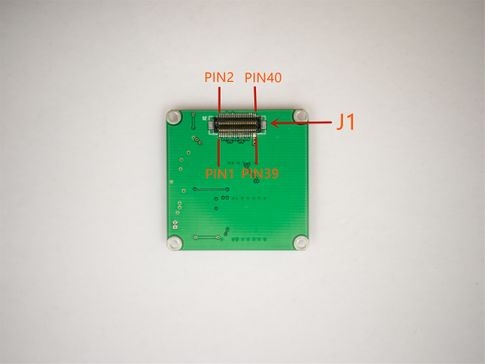

Adapter Board for Rockchip Description

1 Introduction

Rockchip Board can be connected with the Firefly-RK3399,NanoPi and AI0-3288C

- Rockchip Board connect the raspberry pi:

Connect J3 interface and MIPI-CS interface on raspberry pi with 0.5mm 30 pin spacing FFC dissimilar wire

2 Adapter Board Diagram, Layout

- J2 pin list

| 1 | GND |

| 2 | MIPI_L0_N |

| 3 | MIPI_L0_P |

| 4 | GND |

| 5 | MIPI_CK_N |

| 6 | MIPI_CK_P |

| 7 | GND |

| 8 | MIPI_L1_1 |

| 9 | MIPI_L1_P |

| 10 | GND |

| 11 | MIPI_L2_N |

| 12 | MIPI_L2_P |

| 13 | GND |

| 14 | MIPI_L3_N |

| 15 | MIPI_L4_P |

| 16 | GND |

| 17 | MIPI_MCLK0 |

| 18 | GND |

| 19 | GPIOx |

| 20 | MIPI_RST |

| 21 | SCL_3.3V |

| 22 | SDA_3.3V |

| 23 | GND |

| 24 | RESERVE, Not Connected |

| 25 | GND |

| 26 | VCC5V |

| 27 | RESERVE, Not Connected |

| 28 | RESERVE, Not Connected |

| 29 | RESERVE, Not Connected |

| 30 | RESERVE, Not Connected |

- J3 pin list

| 1 | GND |

| 2 | MIPI_L0_N |

| 3 | MIPI_L0_P |

| 4 | GND |

| 5 | MIPI_CK_N |

| 6 | MIPI_CK_P |

| 7 | GND |

| 8 | MIPI_L1_N |

| 9 | MIPI_L1_P |

| 10 | GND |

| 11 | MIPI_L2_N |

| 12 | MIPI_L2_P |

| 13 | GND |

| 14 | MIPI_L3_N |

| 15 | MIPI_L3_P |

| 16 | GND |

| 17 | MIPI_MCLK0 |

| 18 | GND |

| 19 | GPIOx |

| 20 | MIPI_RST |

| 21 | SDA_3.3V |

| 22 | SCL_3.3V |

| 23 | RESERVE, Not Connected |

| 24 | RESERVE, Not Connected |

| 25 | RESERVE, Not Connected |

| 26 | RESERVE, Not Connected |

| 27 | RESERVE, Not Connected |

| 28 | GND |

| 29 | GND |

| 30 | VCC5V |

- J4 pin list

| 1 | MIPI_L0_N |

| 2 | MIPI_L0_P |

| 3 | GND |

| 4 | MIPI_L1_N |

| 5 | MIPI_L1_P |

| 6 | GND |

| 7 | MIPI_CK_N |

| 8 | MIPI_CK_P |

| 9 | GND |

| 10 | MIPI_L2_N |

| 11 | MIPI_L2_P |

| 12 | GND |

| 13 | MIPI_L3_N |

| 14 | MIPI_L4_P |

| 15 | GND |

| 16 | MIPI_MCLK0 |

| 17 | GND |

| 18 | GPIOx |

| 19 | MIPI_RST |

| 20 | SCL_3.3V |

| 21 | SDA_3.3V |

| 22 | MIPI_PWR |

| 23 | CIF_PWR |

| 24 | VCC5V |