Difference between revisions of "Adapter Board for Rockchip/zh"

Jump to navigation

Jump to search

m (Jinpeng moved page Adapter Board+for+Rockchip/zh to Adapter Board for Rockchip/zh) |

|||

| Line 1: | Line 1: | ||

[http://wiki.veye.cc/index.php/Adapter_Board_for_Rockchip English] | [http://wiki.veye.cc/index.php/Adapter_Board_for_Rockchip English] | ||

| + | |||

| + | '''<big>Rockchip转接板使用说明</big>''' | ||

| + | |||

| + | === 概述 === | ||

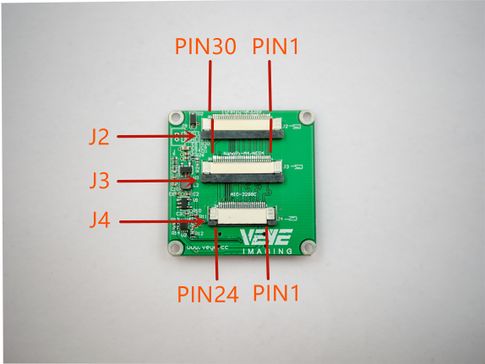

| + | [[File:VEYENanoPi&Firefly Adapter ROCK.jpg|thumb|485x485px|用户接口实物图(前视图)]] | ||

| + | |||

| + | === Rockchip转接板接口布局 === | ||

| + | |||

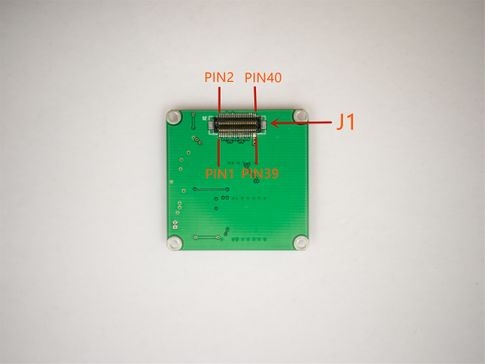

| + | * [[File:VEYENanoPi&Firefly Adapter B .jpg|thumb|485x485px|用户接口实物图(后视图)]]'''用户接口,板间连接器J2引脚列表''' | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |1 | ||

| + | |GND | ||

| + | |2 | ||

| + | |MIPI_L0_N | ||

| + | |- | ||

| + | |3 | ||

| + | |MIPI_L0_P | ||

| + | |4 | ||

| + | |GND | ||

| + | |- | ||

| + | |5 | ||

| + | |MIPI_CK_N | ||

| + | |6 | ||

| + | |MIPI_CK_P | ||

| + | |- | ||

| + | |7 | ||

| + | |GND | ||

| + | |8 | ||

| + | |MIPI_L1_N | ||

| + | |- | ||

| + | |9 | ||

| + | |MIPI_L1_P | ||

| + | |10 | ||

| + | |GND | ||

| + | |- | ||

| + | |11 | ||

| + | |MIPI_L2_N | ||

| + | |12 | ||

| + | |MIPI_L2_P | ||

| + | |- | ||

| + | |13 | ||

| + | |GND | ||

| + | |14 | ||

| + | |MIPI_L3_N | ||

| + | |- | ||

| + | |15 | ||

| + | |MIPI_L3_P | ||

| + | |16 | ||

| + | |GND | ||

| + | |- | ||

| + | |17 | ||

| + | |MIPI_MCLK0 | ||

| + | |18 | ||

| + | |GND | ||

| + | |- | ||

| + | |19 | ||

| + | |GPIOx | ||

| + | |20 | ||

| + | |MIPI_RST | ||

| + | |- | ||

| + | |21 | ||

| + | |MIPI_SCL_1V8 | ||

| + | |22 | ||

| + | |MIPI_SDA_1V8 | ||

| + | |- | ||

| + | |23 | ||

| + | |GND | ||

| + | |24 | ||

| + | |RESERVE, Not Connected | ||

| + | |- | ||

| + | |25 | ||

| + | |GND | ||

| + | |26 | ||

| + | |VCC5V | ||

| + | |- | ||

| + | |27 | ||

| + | |RESERVE, Not Connected | ||

| + | |28 | ||

| + | |RESERVE, Not Connected | ||

| + | |- | ||

| + | |29 | ||

| + | |RESERVE, Not Connected | ||

| + | |30 | ||

| + | |RESERVE, Not Connected | ||

| + | |} | ||

| + | |||

| + | * '''用户接口,板间连接器J3引脚列表''' | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |1 | ||

| + | |GND | ||

| + | |2 | ||

| + | |MIPI_L0_N | ||

| + | |- | ||

| + | |3 | ||

| + | |MIPI_L0_P | ||

| + | |4 | ||

| + | |GND | ||

| + | |- | ||

| + | |5 | ||

| + | |MIPI_CK_N | ||

| + | |6 | ||

| + | |MIPI_CK_P | ||

| + | |- | ||

| + | |7 | ||

| + | |GND | ||

| + | |8 | ||

| + | |MIPI_L1_N | ||

| + | |- | ||

| + | |9 | ||

| + | |MIPI_L1_P | ||

| + | |10 | ||

| + | |GND | ||

| + | |- | ||

| + | |11 | ||

| + | |MIPI_L2_N | ||

| + | |12 | ||

| + | |MIPI_L2_P | ||

| + | |- | ||

| + | |13 | ||

| + | |GND | ||

| + | |14 | ||

| + | |MIPI_L3_N | ||

| + | |- | ||

| + | |15 | ||

| + | |MIPI_L3_P | ||

| + | |16 | ||

| + | |GND | ||

| + | |- | ||

| + | |17 | ||

| + | |MIPI_MCLK0 | ||

| + | |18 | ||

| + | |GND | ||

| + | |- | ||

| + | |19 | ||

| + | |GPIOx | ||

| + | |20 | ||

| + | |MIPI_RST | ||

| + | |- | ||

| + | |21 | ||

| + | |MIPI_SDA_1V8 | ||

| + | |22 | ||

| + | |MIPI_SCL_1V8 | ||

| + | |- | ||

| + | |23 | ||

| + | |RESERVE, Not Connected | ||

| + | |24 | ||

| + | |RESERVE, Not Connected | ||

| + | |- | ||

| + | |25 | ||

| + | |RESERVE, Not Connected | ||

| + | |26 | ||

| + | |RESERVE, Not Connected | ||

| + | |- | ||

| + | |27 | ||

| + | |RESERVE, Not Connected | ||

| + | |28 | ||

| + | |GND | ||

| + | |- | ||

| + | |29 | ||

| + | |GND | ||

| + | |30 | ||

| + | |VCC5V | ||

| + | |} | ||

| + | |||

| + | * '''用户接口,板间连接器J4引脚列表''' | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |1 | ||

| + | |MIPI_L0_N | ||

| + | |2 | ||

| + | |MIPI_L0_P | ||

| + | |- | ||

| + | |3 | ||

| + | |GND | ||

| + | |4 | ||

| + | |MIPI_L1_N | ||

| + | |- | ||

| + | |5 | ||

| + | |MIPI_L1_P | ||

| + | |6 | ||

| + | |GND | ||

| + | |- | ||

| + | |7 | ||

| + | |MIPI_CK_N | ||

| + | |8 | ||

| + | |MIPI_CK_P | ||

| + | |- | ||

| + | |9 | ||

| + | |GND | ||

| + | |10 | ||

| + | |MIPI_L2_N | ||

| + | |- | ||

| + | |11 | ||

| + | |MIPI_L2_P | ||

| + | |12 | ||

| + | |GND | ||

| + | |- | ||

| + | |13 | ||

| + | |MIPI_L3_N | ||

| + | |14 | ||

| + | |MIPI_L3_P | ||

| + | |- | ||

| + | |15 | ||

| + | |GND | ||

| + | |16 | ||

| + | |MIPI_MCLK0 | ||

| + | |- | ||

| + | |17 | ||

| + | |GND | ||

| + | |18 | ||

| + | |GPIOx | ||

| + | |- | ||

| + | |19 | ||

| + | |MIPI_RST | ||

| + | |20 | ||

| + | |MIPI_SCL_1V8 | ||

| + | |- | ||

| + | |21 | ||

| + | |MIPI_SDA_1V8 | ||

| + | |22 | ||

| + | |MIPI_PWR | ||

| + | |- | ||

| + | |23 | ||

| + | |CIF_PWR | ||

| + | |24 | ||

| + | |VCC5V | ||

| + | |} | ||

Revision as of 04:53, 25 July 2019

Rockchip转接板使用说明

1 概述

2 Rockchip转接板接口布局

- 用户接口,板间连接器J2引脚列表

| 1 | GND | 2 | MIPI_L0_N |

| 3 | MIPI_L0_P | 4 | GND |

| 5 | MIPI_CK_N | 6 | MIPI_CK_P |

| 7 | GND | 8 | MIPI_L1_N |

| 9 | MIPI_L1_P | 10 | GND |

| 11 | MIPI_L2_N | 12 | MIPI_L2_P |

| 13 | GND | 14 | MIPI_L3_N |

| 15 | MIPI_L3_P | 16 | GND |

| 17 | MIPI_MCLK0 | 18 | GND |

| 19 | GPIOx | 20 | MIPI_RST |

| 21 | MIPI_SCL_1V8 | 22 | MIPI_SDA_1V8 |

| 23 | GND | 24 | RESERVE, Not Connected |

| 25 | GND | 26 | VCC5V |

| 27 | RESERVE, Not Connected | 28 | RESERVE, Not Connected |

| 29 | RESERVE, Not Connected | 30 | RESERVE, Not Connected |

- 用户接口,板间连接器J3引脚列表

| 1 | GND | 2 | MIPI_L0_N |

| 3 | MIPI_L0_P | 4 | GND |

| 5 | MIPI_CK_N | 6 | MIPI_CK_P |

| 7 | GND | 8 | MIPI_L1_N |

| 9 | MIPI_L1_P | 10 | GND |

| 11 | MIPI_L2_N | 12 | MIPI_L2_P |

| 13 | GND | 14 | MIPI_L3_N |

| 15 | MIPI_L3_P | 16 | GND |

| 17 | MIPI_MCLK0 | 18 | GND |

| 19 | GPIOx | 20 | MIPI_RST |

| 21 | MIPI_SDA_1V8 | 22 | MIPI_SCL_1V8 |

| 23 | RESERVE, Not Connected | 24 | RESERVE, Not Connected |

| 25 | RESERVE, Not Connected | 26 | RESERVE, Not Connected |

| 27 | RESERVE, Not Connected | 28 | GND |

| 29 | GND | 30 | VCC5V |

- 用户接口,板间连接器J4引脚列表

| 1 | MIPI_L0_N | 2 | MIPI_L0_P |

| 3 | GND | 4 | MIPI_L1_N |

| 5 | MIPI_L1_P | 6 | GND |

| 7 | MIPI_CK_N | 8 | MIPI_CK_P |

| 9 | GND | 10 | MIPI_L2_N |

| 11 | MIPI_L2_P | 12 | GND |

| 13 | MIPI_L3_N | 14 | MIPI_L3_P |

| 15 | GND | 16 | MIPI_MCLK0 |

| 17 | GND | 18 | GPIOx |

| 19 | MIPI_RST | 20 | MIPI_SCL_1V8 |

| 21 | MIPI_SDA_1V8 | 22 | MIPI_PWR |

| 23 | CIF_PWR | 24 | VCC5V |