Difference between revisions of "FPD-LINK3-2RX Data Sheet index"

Jump to navigation

Jump to search

| (30 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

<big><big><big>'''FPD-LINK3-2RX Data Sheet (FPD-LINK3-2RX数据手册)'''</big></big></big> | <big><big><big>'''FPD-LINK3-2RX Data Sheet (FPD-LINK3-2RX数据手册)'''</big></big></big> | ||

| − | |||

| − | |||

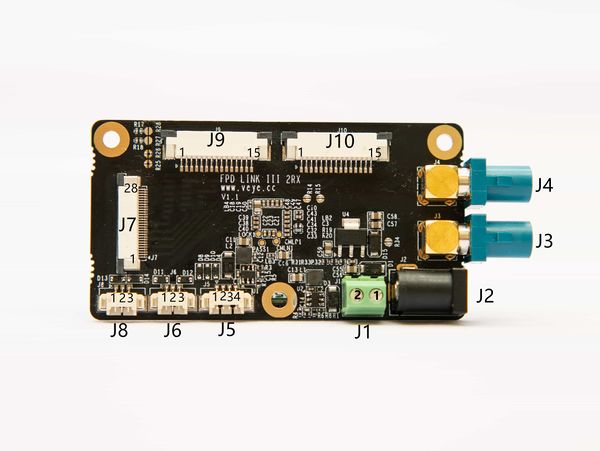

==Product Picture(产品图片)== | ==Product Picture(产品图片)== | ||

| Line 9: | Line 7: | ||

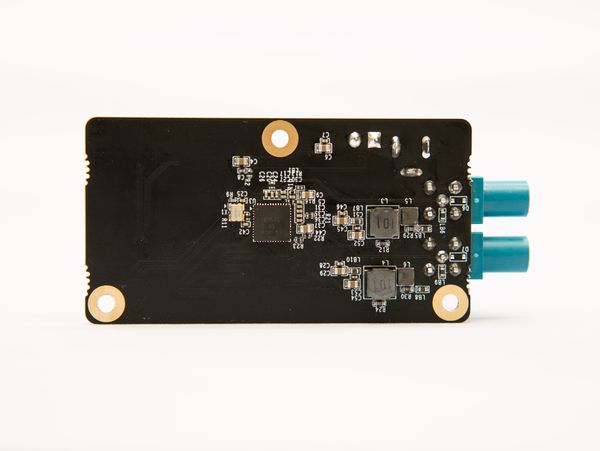

|'''BACK VIEW / 背面图片''' | |'''BACK VIEW / 背面图片''' | ||

|- | |- | ||

| − | |'''FPD-LINK3- | + | |'''FPD-LINK3-2RX''' |

|[[File:FPD-LINK3-2RX 03.jpg|alt=|center|thumb|200x200px]] | |[[File:FPD-LINK3-2RX 03.jpg|alt=|center|thumb|200x200px]] | ||

|[[File:FPD-LINK3-2RX 04.jpg|alt=|center|thumb|200x200px]] | |[[File:FPD-LINK3-2RX 04.jpg|alt=|center|thumb|200x200px]] | ||

| + | |} | ||

| + | |||

| + | == Thechnical Detail (技术规格) == | ||

| + | |||

| + | {| class="wikitable" | ||

| + | | colspan="2" |'''Thechnical Detail (技术规格)''' | ||

| + | |- | ||

| + | | colspan="2" |'''Dual 2 MP FPD-Link III deserializer''' | ||

| + | |- | ||

| + | |IC PART NO. | ||

| + | |[https://www.ti.com/product/DS90UB954-Q1?keyMatch=DS90UB954-Q1&tisearch=Search-EN-everything DS90UB954-Q1] / [https://www.ti.com/product/TDES954 TDES954RGZT] | ||

| + | |- | ||

| + | |Function | ||

| + | |Deserializer | ||

| + | |- | ||

| + | |Input Compatibility | ||

| + | |[https://www.ti.com/interface/high-speed-serdes/fpd-link-serdes/overview.html FPD-Link III LVDS] / [https://www.ti.com/interface/high-speed-serdes/v3link-serdes/overview.html V3Link SerDes] | ||

| + | |- | ||

| + | |Output Compatibility | ||

| + | |MIPI CSI-2 | ||

| + | |- | ||

| + | |REFCLK | ||

| + | |25MHz | ||

| + | |- | ||

| + | | colspan="2" |'''Interface''' | ||

| + | |- | ||

| + | |MIPI Output | ||

| + | |MIPI CSI-2 2lane ,J9 Support | ||

| + | MIPI CSI-2 4lane ,J7 Support | ||

| + | |- | ||

| + | |MIPI Output Connector | ||

| + | |FFC socket(J7 / J9) | ||

| + | |- | ||

| + | |LVDS Input | ||

| + | | FPD-Link III LVDS | ||

| + | |- | ||

| + | |LVDS Input Connector | ||

| + | |FAKRA Z Compatibility * 2, '''J3(Port 0), J4(Port 1)''' | ||

| + | |- | ||

| + | |MPIO | ||

| + | |Up to 7 Multi-function IO | ||

| + | |- | ||

| + | | colspan="2" |'''Device Functional Modes''' | ||

| + | |- | ||

| + | |FPD-Link III Operating Mode | ||

| + | |CSI-2 Mode (DS90UB953-Q1 and DS90UB935-Q1 compatible) | ||

| + | |- | ||

| + | |Forward Channel Mode | ||

| + | |Synchronous Mode | ||

| + | |- | ||

| + | |Back Channel Mode | ||

| + | |Synchronous Mode | ||

| + | |- | ||

| + | |FPD-Link Line Rate | ||

| + | |4.0 Gbps | ||

| + | |- | ||

| + | |Back Channel Rate | ||

| + | |50 Mbps | ||

| + | |- | ||

| + | | colspan="2" |'''General''' | ||

| + | |- | ||

| + | |Operating Conditions | ||

| + | ('''Bare PCB''') | ||

| + | |Operating guarantee temperature:'''-20℃~85℃''', Humidity 95% or less, non-condensing | ||

| + | |- | ||

| + | |DC Power Supply | ||

| + | |DC 12V(J1 / J2 Input) | ||

| + | |- | ||

| + | |POC Power Supply | ||

| + | |DC 9.4V(J3 / J4 Output) | ||

| + | |- | ||

| + | |Dimension | ||

| + | |75mm*40mm | ||

|} | |} | ||

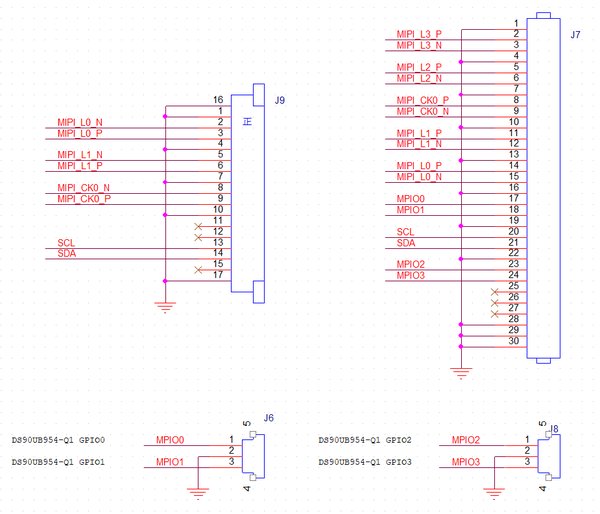

[[File:FPD-LINK3-2RX 01 IF.jpg|alt=|thumb|600x600px|FPD-LINK3-2RX Pin List]] | [[File:FPD-LINK3-2RX 01 IF.jpg|alt=|thumb|600x600px|FPD-LINK3-2RX Pin List]] | ||

| + | [[File:FPD LINK III-2RX PIN.png|alt=|thumb|600x600px|FPD-LINK3-2RX Pin List]] | ||

| − | == | + | ==Board Pinlist(接口和引脚说明)== |

{| class="wikitable" | {| class="wikitable" | ||

| colspan="3" |'''J1:12V PWR IN(12V电源输入)''' | | colspan="3" |'''J1:12V PWR IN(12V电源输入)''' | ||

| Line 32: | Line 104: | ||

|} | |} | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | |'''J2: 12V PWR | + | | colspan="2" |'''J2: 12V PWR IN(12V电源输入)''' |

| − | ''' | + | |- |

| − | |[[File:Polarity diagram.png|center|thumb| | + | |'''Connector(接插件)''' |

| − | | colspan=" | + | |'''Interface Definition(接口定义)''' |

| − | ''' | + | |- |

| − | |[[File:Polarity diagram.png|link=http://wiki.veye.cc/index.php/File:Polarity%20diagram.png|center|thumb| | + | |DC JACK |

| + | |[[File:Polarity diagram.png|center|thumb|200x200px|'''+:12VIN / -:GND'''|alt=]] | ||

| + | |} | ||

| + | {| class="wikitable" | ||

| + | | colspan="2" |'''J3 J4: POC interface(POC接口)''' | ||

| + | '''J3(Port 0 / P0)''' | ||

| + | |||

| + | '''J4(Port 1 / P1)''' | ||

| + | |- | ||

| + | |'''Connector(接插件)''' | ||

| + | |'''Interface Definition(接口定义)''' | ||

| + | |- | ||

| + | |FAKRA Z | ||

| + | |[[File:Polarity diagram.png|link=http://wiki.veye.cc/index.php/File:Polarity%20diagram.png|center|thumb|200x200px|'''+:POC signal / -:GND'''|alt=]] | ||

|} | |} | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 47: | Line 132: | ||

|- | |- | ||

|1 | |1 | ||

| − | | | + | |MPIO4 |

| − | | | + | |3.3V LEVEL |

|- | |- | ||

|2 | |2 | ||

| − | | | + | |MPIO5 |

| − | | | + | |3.3V LEVEL |

|- | |- | ||

|3 | |3 | ||

| − | | | + | |MPIO6 |

| − | | | + | |3.3V LEVEL |

|- | |- | ||

|4 | |4 | ||

| Line 74: | Line 159: | ||

|- | |- | ||

|1 | |1 | ||

| − | | | + | |MPIO0 |

| − | | | + | |3.3V LEVEL |

|1 | |1 | ||

| − | | | + | |MPIO2 |

| − | | | + | |3.3V LEVEL |

|- | |- | ||

|2 | |2 | ||

| Line 88: | Line 173: | ||

|- | |- | ||

|3 | |3 | ||

| − | | | + | |MPIO1 |

| − | | | + | |3.3V LEVEL |

|3 | |3 | ||

| − | | | + | |MPIO3 |

| − | | | + | |3.3V LEVEL |

|} | |} | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | | colspan="3" |''' | + | | colspan="3" |'''J7: Connected to ADP-N2/N3''' |

|- | |- | ||

|'''<small>Pin NO.(引脚号)</small>''' | |'''<small>Pin NO.(引脚号)</small>''' | ||

| Line 166: | Line 251: | ||

|- | |- | ||

|17 | |17 | ||

| − | | | + | |MPIO0 |

| | | | ||

|- | |- | ||

|18 | |18 | ||

| − | | | + | |MPIO1 |

| | | | ||

|- | |- | ||

| Line 190: | Line 275: | ||

|- | |- | ||

|23 | |23 | ||

| − | | | + | |MPIO2 |

| − | | | + | |3.3V LEVEL |

|- | |- | ||

|24 | |24 | ||

| − | | | + | |MPIO3 |

| − | | | + | |3.3V LEVEL |

|- | |- | ||

|25 | |25 | ||

| Line 213: | Line 298: | ||

| | | | ||

|} | |} | ||

| + | [[File:FPD-LINK3-2RX 02.jpg|alt=|thumb|600x600px|FPD-LINK3-2RX BACK]] | ||

{| class="wikitable" | {| class="wikitable" | ||

| colspan="3" |'''J9:CSI-2''' | | colspan="3" |'''J9:CSI-2''' | ||

| Line 330: | Line 416: | ||

|} | |} | ||

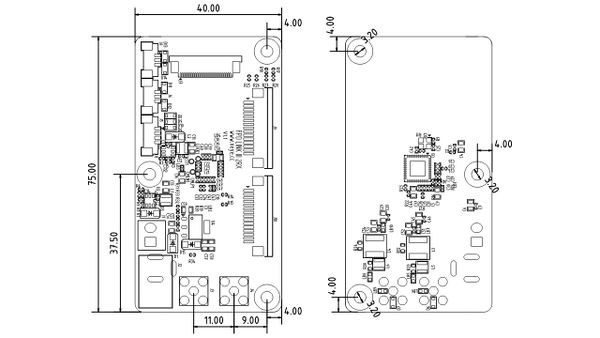

==Board Dimension(板子尺寸)== | ==Board Dimension(板子尺寸)== | ||

| − | + | [[File:FPD-LINK3-2RX JPG DWG.jpg|alt=|none|thumb|600x600px|FPD-LINK3-2RX CAD / unit:mm]] | |

| + | [[Media:FPD-LINK3-2RX DWG.dwg|Download dwg file here]] | ||

| + | == PCBA 3D STP File == | ||

| + | [[Media:3D FPD-LINK3-2RX.zip|download 3D STP file]] | ||

Latest revision as of 02:19, 25 December 2023

FPD-LINK3-2RX Data Sheet (FPD-LINK3-2RX数据手册)

1 Product Picture(产品图片)

| PART NUMBER / 型号 | FRONT VIEW / 正面图片 | BACK VIEW / 背面图片 |

| FPD-LINK3-2RX |

2 Thechnical Detail (技术规格)

| Thechnical Detail (技术规格) | |

| Dual 2 MP FPD-Link III deserializer | |

| IC PART NO. | DS90UB954-Q1 / TDES954RGZT |

| Function | Deserializer |

| Input Compatibility | FPD-Link III LVDS / V3Link SerDes |

| Output Compatibility | MIPI CSI-2 |

| REFCLK | 25MHz |

| Interface | |

| MIPI Output | MIPI CSI-2 2lane ,J9 Support

MIPI CSI-2 4lane ,J7 Support |

| MIPI Output Connector | FFC socket(J7 / J9) |

| LVDS Input | FPD-Link III LVDS |

| LVDS Input Connector | FAKRA Z Compatibility * 2, J3(Port 0), J4(Port 1) |

| MPIO | Up to 7 Multi-function IO |

| Device Functional Modes | |

| FPD-Link III Operating Mode | CSI-2 Mode (DS90UB953-Q1 and DS90UB935-Q1 compatible) |

| Forward Channel Mode | Synchronous Mode |

| Back Channel Mode | Synchronous Mode |

| FPD-Link Line Rate | 4.0 Gbps |

| Back Channel Rate | 50 Mbps |

| General | |

| Operating Conditions

(Bare PCB) |

Operating guarantee temperature:-20℃~85℃, Humidity 95% or less, non-condensing |

| DC Power Supply | DC 12V(J1 / J2 Input) |

| POC Power Supply | DC 9.4V(J3 / J4 Output) |

| Dimension | 75mm*40mm |

3 Board Pinlist(接口和引脚说明)

| J1:12V PWR IN(12V电源输入) | ||

| Pin NO.(引脚号) | NAME(名称) | Remarks(说明) |

| 1 | 12VIN | |

| 2 | GND | |

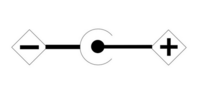

| J2: 12V PWR IN(12V电源输入) | |

| Connector(接插件) | Interface Definition(接口定义) |

| DC JACK | |

| J3 J4: POC interface(POC接口)

J3(Port 0 / P0) J4(Port 1 / P1) | |

| Connector(接插件) | Interface Definition(接口定义) |

| FAKRA Z | |

| J5 : RESERVE(预留未用) | ||

| Pin NO.(引脚号) | NAME(名称) | Remarks(说明) |

| 1 | MPIO4 | 3.3V LEVEL |

| 2 | MPIO5 | 3.3V LEVEL |

| 3 | MPIO6 | 3.3V LEVEL |

| 4 | GND | |

| J6 : | J8: | ||||

| Pin NO.(引脚号) | NAME(名称) | Remarks(说明) | Pin NO.(引脚号) | NAME(名称) | Remarks(说明) |

| 1 | MPIO0 | 3.3V LEVEL | 1 | MPIO2 | 3.3V LEVEL |

| 2 | GND | 2 | GND | ||

| 3 | MPIO1 | 3.3V LEVEL | 3 | MPIO3 | 3.3V LEVEL |

| J7: Connected to ADP-N2/N3 | ||

| Pin NO.(引脚号) | NAME(名称) | Remarks(说明) |

| 1 | GND | |

| 2 | MIPI_L3_P | |

| 3 | MIPI_L3_N | |

| 4 | GND | |

| 5 | MIPI_L2_P | |

| 6 | MIPI_L2_N | |

| 7 | GND | |

| 8 | MIPI_CK_P | |

| 9 | MIPI_CK_N | |

| 10 | GND | |

| 11 | MIPI_L1_P | |

| 12 | MIPI_L1_N | |

| 13 | GND | |

| 14 | MIPI_L0_P | |

| 15 | MIPI_L0_N | |

| 16 | GND | |

| 17 | MPIO0 | |

| 18 | MPIO1 | |

| 19 | GND | |

| 20 | SCL | 3.3V LEVEL |

| 21 | SDA | 3.3V LEVEL |

| 22 | GND | |

| 23 | MPIO2 | 3.3V LEVEL |

| 24 | MPIO3 | 3.3V LEVEL |

| 25 | NC | |

| 26 | NC | |

| 27 | NC | |

| 28 | GND | |

| J9:CSI-2 | J10:RESERVE(预留未用) | ||||

| Pin NO.(引脚号) | NAME(名称) | Remarks(说明) | Pin NO.(引脚号) | NAME(名称) | Remarks(说明) |

| 1 | GND | 1 | GND | ||

| 2 | MIPI_L0_N | 2 | MIPI_L0_N | ||

| 3 | MIPI_L0_P | 3 | MIPI_L0_P | ||

| 4 | GND | 4 | GND | ||

| 5 | MIPI_L1_N | 5 | MIPI_L1_N | ||

| 6 | MIPI_L1_P | 6 | MIPI_L1_P | ||

| 7 | GND | 7 | GND | ||

| 8 | MIPI_CK_N | 8 | MIPI_CK_N | ||

| 9 | MIPI_CK_P | 9 | MIPI_CK_P | ||

| 10 | GND | 10 | GND | ||

| 11 | NC | 11 | NC | ||

| 12 | NC | 12 | NC | ||

| 13 | SCL | 3.3V LEVEL | 13 | SCL | 3.3V LEVEL |

| 14 | SDA | 3.3V LEVEL | 14 | SDA | 3.3V LEVEL |

| 15 | NC | 15 | NC | ||