Difference between revisions of "ADP-N5 Adapter Board Data Sheet"

Jump to navigation

Jump to search

(Created page with "<big><big><big>'''Adapter Board:ADP-N1-V2.0 Data Sheet'''</big></big></big> ==Product Introduction(产品介绍)== ADP-N1-V2.0 is a camera interposer module for NVIDIA Je...") |

|||

| (7 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

| − | <big><big><big>''' | + | <big><big><big>'''Addon Board:ADP-N5 Data Sheet'''</big></big></big> |

==Product Introduction(产品介绍)== | ==Product Introduction(产品介绍)== | ||

| − | ADP- | + | ADP-N5 is a add on module for NVIDIA Jetson AGX Xavier、AGX Orin and TX2 DevKit. |

| − | ADP- | + | ADP-N5 support external 12V power supply function or 3.3V power supply from AGX Xavier / Orin / TX2 DevKit. |

When 12V power supply is used, 3.3V power supply of the main board will be automatically cut off. | When 12V power supply is used, 3.3V power supply of the main board will be automatically cut off. | ||

| − | ADP- | + | ADP-N5是NVIDIA Jetson AGX Xavier、AGX Orin或者TX2开发套件的摄像头转接板。 |

| − | ADP- | + | ADP-N5支持外部12V供电或者使用AGX Xavier / Orin / TX2开发套件的3.3V供电。当使用12V供电时,自动切断主板3.3V供电。 |

| − | |||

| − | |||

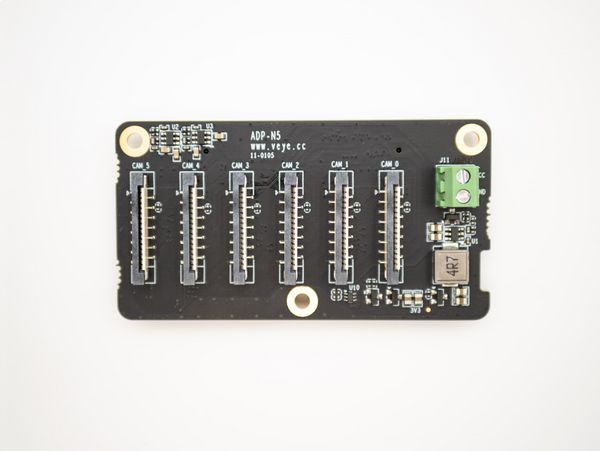

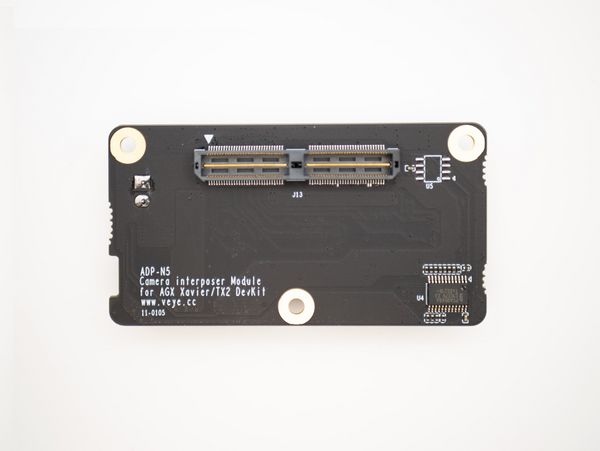

==Product Picture(产品图片)== | ==Product Picture(产品图片)== | ||

| Line 19: | Line 17: | ||

|'''FRONT VIEW / 正面图片''' | |'''FRONT VIEW / 正面图片''' | ||

|'''BACK VIEW / 背面图片''' | |'''BACK VIEW / 背面图片''' | ||

| − | |||

|- | |- | ||

| − | |'''ADP- | + | |'''ADP-N5''' |

| − | |[[File:ADP- | + | |[[File:ADP-N5-01.jpg|alt=|center|thumb|200x200px|'''ADP-N5''']] |

| − | |[[File:ADP- | + | |[[File:ADP-N5-02.jpg|alt=|center|thumb|200x200px|'''ADP-N5''']] |

| − | |||

|} | |} | ||

| − | [[File:ADP- | + | [[File:ADP-N5-04.jpg|alt=|thumb|600x600px|ADP-N5]] |

| − | [[File:ADP- | + | [[File:ADP-N5-03.jpg|alt=|thumb|600x600px|ADP-N5]] |

==Adapter Board Pinlist(接口和引脚说明)== | ==Adapter Board Pinlist(接口和引脚说明)== | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{| class="wikitable" | {| class="wikitable" | ||

| colspan="3" |'''J11''' | | colspan="3" |'''J11''' | ||

| Line 76: | Line 34: | ||

|- | |- | ||

|1 | |1 | ||

| − | | | + | |VCC |

|DC12V INPUT(DC12V输入) | |DC12V INPUT(DC12V输入) | ||

|- | |- | ||

|2 | |2 | ||

|GND | |GND | ||

| − | | | + | |GND (电源地) |

|} | |} | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | + | | colspan="13" |'''CAM0 / CAM1 / CAM2 / CAM3 / CAM4 / CAM5''' | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | | colspan="13" |''' | ||

|- | |- | ||

| rowspan="2" |'''<small>Pin NO.</small>''' | | rowspan="2" |'''<small>Pin NO.</small>''' | ||

| − | | colspan="2" |'''<small> | + | | colspan="2" |'''<small>CAM0</small>''' |

| − | | colspan="2" |'''<small> | + | | colspan="2" |'''<small>CAM1</small>''' |

| − | | colspan="2" |'''<small> | + | | colspan="2" |'''<small>CAM2</small>''' |

| − | | colspan="2" |'''<small> | + | | colspan="2" |'''<small>CAM3</small>''' |

| − | | colspan="2" |'''<small> | + | | colspan="2" |'''<small>CAM4</small>''' |

| − | | colspan="2" |'''<small> | + | | colspan="2" |'''<small>CAM5</small>''' |

|- | |- | ||

|'''<small>NAME</small>''' | |'''<small>NAME</small>''' | ||

| Line 127: | Line 66: | ||

|- | |- | ||

|<small>1</small> | |<small>1</small> | ||

| − | |<small> | + | |<small>VCC3V3</small> |

| | | | ||

| − | |<small> | + | |<small>VCC3V3</small> |

| | | | ||

| − | |<small> | + | |<small>VCC3V3</small> |

| | | | ||

| − | |<small> | + | |<small>VCC3V3</small> |

| | | | ||

| − | |<small> | + | |<small>VCC3V3</small> |

| | | | ||

| − | |<small> | + | |<small>VCC3V3</small> |

| | | | ||

|- | |- | ||

|<small>2</small> | |<small>2</small> | ||

| − | |<small> | + | |<small>CSI_0_SDA</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_1_SDA</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_2_SDA</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_3_SDA</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_4_SDA</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_5_SDA</small> |

| | | | ||

|- | |- | ||

|<small>3</small> | |<small>3</small> | ||

| − | |<small> | + | |<small>CSI_0_SCL</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_1_SCL</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_2_SCL</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_3_SCL</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_4_SCL</small> |

| | | | ||

| − | |<small> | + | |<small>CSI_5_SCL</small> |

| | | | ||

|- | |- | ||

|<small>4</small> | |<small>4</small> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|<small>NC</small> | |<small>NC</small> | ||

| | | | ||

| Line 195: | Line 120: | ||

|<small>NC</small> | |<small>NC</small> | ||

| | | | ||

| + | |- | ||

| + | |<small>5</small> | ||

| + | |<small>ENABLE_1</small> | ||

| + | |3V3 | ||

| + | |<small>ENABLE_1</small> | ||

| + | |3V3 | ||

| + | |<small>ENABLE_1</small> | ||

| + | |3V3 | ||

| + | |<small>ENABLE_1</small> | ||

| + | |3V3 | ||

| + | |<small>ENABLE_1</small> | ||

| + | |3V3 | ||

| + | |<small>ENABLE_1</small> | ||

| + | |3V3 | ||

|- | |- | ||

|<small>6</small> | |<small>6</small> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|<small>GND</small> | |<small>GND</small> | ||

| | | | ||

| Line 224: | Line 149: | ||

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>7</small> |

| − | | | + | |CSI0_CLK_P |

| | | | ||

| − | | | + | |CSI1_CLK_P |

| | | | ||

| − | | | + | |CSI2_CLK_P |

| | | | ||

| − | | | + | |CSI3_CLK_P |

| | | | ||

| − | | | + | |CSI4_CLK_P |

| | | | ||

| − | | | + | |CSI6_CLK_P |

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>8</small> |

| − | | | + | |CSI0_CLK_N |

| | | | ||

| − | | | + | |CSI1_CLK_N |

| | | | ||

| − | | | + | |CSI2_CLK_N |

| | | | ||

| − | | | + | |CSI3_CLK_N |

| | | | ||

| − | | | + | |CSI4_CLK_N |

| | | | ||

| − | | | + | |CSI6_CLK_N |

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>9</small> |

|<small>GND</small> | |<small>GND</small> | ||

| | | | ||

| Line 266: | Line 191: | ||

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>10</small> |

| − | | | + | |CSI0_D1_P |

| | | | ||

| − | | | + | |CSI1_D1_P |

| | | | ||

| − | | | + | |CSI2_D1_P |

| | | | ||

| − | | | + | |CSI3_D1_P |

| | | | ||

| − | | | + | |CSI4_D1_P |

| | | | ||

| − | | | + | |CSI6_D1_P |

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>11</small> |

| − | | | + | |CSI0_D1_N |

| | | | ||

| − | | | + | |CSI1_D1_N |

| | | | ||

| − | | | + | |CSI2_D1_N |

| | | | ||

| − | | | + | |CSI3_D1_N |

| | | | ||

| − | | | + | |CSI4_D1_N |

| | | | ||

| − | | | + | |CSI6_D1_N |

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>12</small> |

|<small>GND</small> | |<small>GND</small> | ||

| | | | ||

| Line 308: | Line 233: | ||

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>13</small> |

| − | | | + | |CSI0_D0_P |

| | | | ||

| − | | | + | |CSI1_D0_P |

| | | | ||

| − | | | + | |CSI2_D0_P |

| | | | ||

| − | | | + | |CSI3_D0_P |

| | | | ||

| − | | | + | |CSI4_D0_P |

| | | | ||

| − | | | + | |CSI6_D0_P |

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>14</small> |

| − | | | + | |CSI0_D0_N |

| | | | ||

| − | | | + | |CSI1_D0_N |

| | | | ||

| − | | | + | |CSI2_D0_N |

| | | | ||

| − | | | + | |CSI3_D0_N |

| | | | ||

| − | | | + | |CSI4_D0_N |

| | | | ||

| − | | | + | |CSI6_D0_N |

| | | | ||

|- | |- | ||

| − | |<small> | + | |<small>15</small> |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|<small>GND</small> | |<small>GND</small> | ||

| | | | ||

| Line 519: | Line 276: | ||

|}<br /> | |}<br /> | ||

{| class="wikitable" | {| class="wikitable" | ||

| − | | colspan="12" |''' | + | | colspan="12" |'''J13''' |

|- | |- | ||

|'''<small>Pin NO.</small>''' | |'''<small>Pin NO.</small>''' | ||

| Line 535: | Line 292: | ||

|- | |- | ||

|<small>1</small> | |<small>1</small> | ||

| − | |<small> | + | |<small>CSI0_D0_P</small> |

| | | | ||

|<small>31</small> | |<small>31</small> | ||

| − | |<small> | + | |<small>CSI2_D1_P</small> |

| | | | ||

|<small>61</small> | |<small>61</small> | ||

| Line 548: | Line 305: | ||

|- | |- | ||

|<small>2</small> | |<small>2</small> | ||

| − | |<small> | + | |<small>CSI1_D0_P</small> |

| | | | ||

|<small>32</small> | |<small>32</small> | ||

| − | |<small> | + | |<small>CSI3_D1_P</small> |

| | | | ||

|<small>62</small> | |<small>62</small> | ||

| Line 561: | Line 318: | ||

|- | |- | ||

|<small>3</small> | |<small>3</small> | ||

| − | |<small> | + | |<small>CSI0_D0_N</small> |

| | | | ||

|<small>33</small> | |<small>33</small> | ||

| − | |<small> | + | |<small>CSI2_D1_N</small> |

| | | | ||

|<small>63</small> | |<small>63</small> | ||

| Line 574: | Line 331: | ||

|- | |- | ||

|<small>4</small> | |<small>4</small> | ||

| − | |<small> | + | |<small>CSI1_D0_N</small> |

| | | | ||

|<small>34</small> | |<small>34</small> | ||

| − | |<small> | + | |<small>CSI3_D1_N</small> |

| | | | ||

|<small>64</small> | |<small>64</small> | ||

| Line 613: | Line 370: | ||

|- | |- | ||

|<small>7</small> | |<small>7</small> | ||

| − | |<small> | + | |<small>CSI0_CLK_P</small> |

| | | | ||

|<small>37</small> | |<small>37</small> | ||

| − | |<small> | + | |<small>CSI4_D0_P</small> |

| | | | ||

|<small>67</small> | |<small>67</small> | ||

| Line 626: | Line 383: | ||

|- | |- | ||

|<small>8</small> | |<small>8</small> | ||

| − | |<small> | + | |<small>CSI1_CLK_P</small> |

| | | | ||

|<small>38</small> | |<small>38</small> | ||

| − | |<small> | + | |<small>CSI6_D0_P</small> |

| | | | ||

|<small>68</small> | |<small>68</small> | ||

| Line 639: | Line 396: | ||

|- | |- | ||

|<small>9</small> | |<small>9</small> | ||

| − | |<small> | + | |<small>CSI0_CLK_N</small> |

| | | | ||

|<small>39</small> | |<small>39</small> | ||

| − | |<small> | + | |<small>CSI4_D0_N</small> |

| | | | ||

|<small>69</small> | |<small>69</small> | ||

| Line 652: | Line 409: | ||

|- | |- | ||

|<small>10</small> | |<small>10</small> | ||

| − | |<small> | + | |<small>CSI1_CLK_N</small> |

| | | | ||

|<small>40</small> | |<small>40</small> | ||

| − | |<small> | + | |<small>CSI6_D0_N</small> |

| | | | ||

|<small>70</small> | |<small>70</small> | ||

| Line 691: | Line 448: | ||

|- | |- | ||

|<small>13</small> | |<small>13</small> | ||

| − | |<small> | + | |<small>CSI0_D1_P</small> |

| | | | ||

|<small>43</small> | |<small>43</small> | ||

| − | |<small> | + | |<small>CSI4_CLK_P</small> |

| | | | ||

|<small>73</small> | |<small>73</small> | ||

| Line 704: | Line 461: | ||

|- | |- | ||

|<small>14</small> | |<small>14</small> | ||

| − | |<small> | + | |<small>CSI1_D1_P</small> |

| | | | ||

|<small>44</small> | |<small>44</small> | ||

| − | |<small> | + | |<small>CSI6_CLK_P</small> |

| | | | ||

|<small>74</small> | |<small>74</small> | ||

| Line 717: | Line 474: | ||

|- | |- | ||

|<small>15</small> | |<small>15</small> | ||

| − | |<small> | + | |<small>CSI0_D1_N</small> |

| | | | ||

|<small>45</small> | |<small>45</small> | ||

| − | |<small> | + | |<small>CSI4_CLK_N</small> |

| | | | ||

|<small>75</small> | |<small>75</small> | ||

| Line 730: | Line 487: | ||

|- | |- | ||

|<small>16</small> | |<small>16</small> | ||

| − | |<small> | + | |<small>CSI1_D1_N</small> |

| | | | ||

|<small>46</small> | |<small>46</small> | ||

| − | |<small> | + | |<small>CSI6_CLK_N</small> |

| | | | ||

|<small>76</small> | |<small>76</small> | ||

| Line 769: | Line 526: | ||

|- | |- | ||

|<small>19</small> | |<small>19</small> | ||

| − | |<small> | + | |<small>CSI2_D0_P</small> |

| | | | ||

|<small>49</small> | |<small>49</small> | ||

| − | |<small> | + | |<small>CSI4_D1_P</small> |

| | | | ||

|<small>79</small> | |<small>79</small> | ||

| Line 778: | Line 535: | ||

| | | | ||

|<small>109</small> | |<small>109</small> | ||

| − | | | + | |NC |

| − | | | + | | |

|- | |- | ||

|<small>20</small> | |<small>20</small> | ||

| − | |<small> | + | |<small>CSI3_D0_P</small> |

| | | | ||

|<small>50</small> | |<small>50</small> | ||

| − | |<small> | + | |<small>CSI6_D1_P</small> |

| | | | ||

|<small>80</small> | |<small>80</small> | ||

| Line 795: | Line 552: | ||

|- | |- | ||

|<small>21</small> | |<small>21</small> | ||

| − | |<small> | + | |<small>CSI2_D0_N</small> |

| | | | ||

|<small>51</small> | |<small>51</small> | ||

| − | |<small> | + | |<small>CSI4_D1_N</small> |

| | | | ||

|<small>81</small> | |<small>81</small> | ||

| Line 808: | Line 565: | ||

|- | |- | ||

|<small>22</small> | |<small>22</small> | ||

| − | |<small> | + | |<small>CSI3_D0_N</small> |

| | | | ||

|<small>52</small> | |<small>52</small> | ||

| − | |<small> | + | |<small>CSI6_D1_N</small> |

| | | | ||

|<small>82</small> | |<small>82</small> | ||

| Line 840: | Line 597: | ||

| | | | ||

|<small>84</small> | |<small>84</small> | ||

| − | | | + | |NC |

| − | | | + | | |

|<small>114</small> | |<small>114</small> | ||

|<small>NC</small> | |<small>NC</small> | ||

| Line 847: | Line 604: | ||

|- | |- | ||

|<small>25</small> | |<small>25</small> | ||

| − | |<small> | + | |<small>CSI2_CLK_P</small> |

| | | | ||

|<small>55</small> | |<small>55</small> | ||

| Line 860: | Line 617: | ||

|- | |- | ||

|<small>26</small> | |<small>26</small> | ||

| − | |<small> | + | |<small>CSI3_CLK_P</small> |

| | | | ||

|<small>56</small> | |<small>56</small> | ||

| Line 866: | Line 623: | ||

| | | | ||

|<small>86</small> | |<small>86</small> | ||

| − | |<small> | + | |<small>NC</small> |

| − | | | + | | |

|<small>116</small> | |<small>116</small> | ||

|<small>GND</small> | |<small>GND</small> | ||

| Line 873: | Line 630: | ||

|- | |- | ||

|<small>27</small> | |<small>27</small> | ||

| − | |<small> | + | |<small>CSI2_CLK_N</small> |

| | | | ||

|<small>57</small> | |<small>57</small> | ||

| Line 886: | Line 643: | ||

|- | |- | ||

|<small>28</small> | |<small>28</small> | ||

| − | |<small> | + | |<small>CSI3_CLK_N</small> |

| | | | ||

|<small>58</small> | |<small>58</small> | ||

| Line 926: | Line 683: | ||

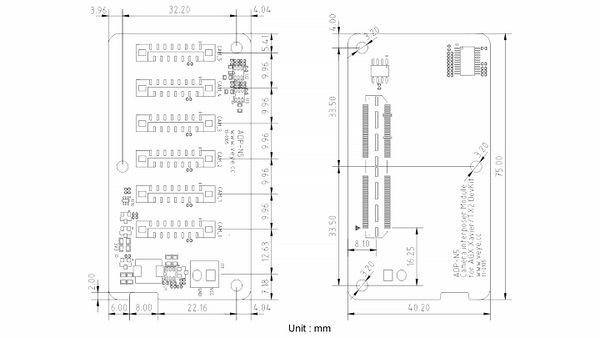

==Adapter Board Dimension(板子尺寸)== | ==Adapter Board Dimension(板子尺寸)== | ||

| − | [[File:ADP- | + | [[File:ADP-N5-V11-0105-2D.jpg|alt=|center|thumb|600x600px]] |

| − | [[Media:ADP- | + | [[Media:ADP-N5-V11-0105-2D.7z|Download 2D file here]] |

== PCBA 3D STP File(PCBA 3D STP文件)== | == PCBA 3D STP File(PCBA 3D STP文件)== | ||

| − | [[Media: | + | [[Media:ADP-N5-V11-0105-3D.7z|Download 3D file here]] |

Latest revision as of 03:49, 21 June 2023

Addon Board:ADP-N5 Data Sheet

1 Product Introduction(产品介绍)

ADP-N5 is a add on module for NVIDIA Jetson AGX Xavier、AGX Orin and TX2 DevKit.

ADP-N5 support external 12V power supply function or 3.3V power supply from AGX Xavier / Orin / TX2 DevKit.

When 12V power supply is used, 3.3V power supply of the main board will be automatically cut off.

ADP-N5是NVIDIA Jetson AGX Xavier、AGX Orin或者TX2开发套件的摄像头转接板。

ADP-N5支持外部12V供电或者使用AGX Xavier / Orin / TX2开发套件的3.3V供电。当使用12V供电时,自动切断主板3.3V供电。

2 Product Picture(产品图片)

| PART NUMBER / 型号 | FRONT VIEW / 正面图片 | BACK VIEW / 背面图片 |

| ADP-N5 |

3 Adapter Board Pinlist(接口和引脚说明)

| J11 | ||

| Pin NO.(引脚号) | NAME(名称) | Remarks(说明) |

| 1 | VCC | DC12V INPUT(DC12V输入) |

| 2 | GND | GND (电源地) |

| CAM0 / CAM1 / CAM2 / CAM3 / CAM4 / CAM5 | ||||||||||||

| Pin NO. | CAM0 | CAM1 | CAM2 | CAM3 | CAM4 | CAM5 | ||||||

| NAME | Remarks | NAME | Remarks | NAME | Remarks | NAME | Remarks | NAME | Remarks | NAME | Remarks | |

| 1 | VCC3V3 | VCC3V3 | VCC3V3 | VCC3V3 | VCC3V3 | VCC3V3 | ||||||

| 2 | CSI_0_SDA | CSI_1_SDA | CSI_2_SDA | CSI_3_SDA | CSI_4_SDA | CSI_5_SDA | ||||||

| 3 | CSI_0_SCL | CSI_1_SCL | CSI_2_SCL | CSI_3_SCL | CSI_4_SCL | CSI_5_SCL | ||||||

| 4 | NC | NC | NC | NC | NC | NC | ||||||

| 5 | ENABLE_1 | 3V3 | ENABLE_1 | 3V3 | ENABLE_1 | 3V3 | ENABLE_1 | 3V3 | ENABLE_1 | 3V3 | ENABLE_1 | 3V3 |

| 6 | GND | GND | GND | GND | GND | GND | ||||||

| 7 | CSI0_CLK_P | CSI1_CLK_P | CSI2_CLK_P | CSI3_CLK_P | CSI4_CLK_P | CSI6_CLK_P | ||||||

| 8 | CSI0_CLK_N | CSI1_CLK_N | CSI2_CLK_N | CSI3_CLK_N | CSI4_CLK_N | CSI6_CLK_N | ||||||

| 9 | GND | GND | GND | GND | GND | GND | ||||||

| 10 | CSI0_D1_P | CSI1_D1_P | CSI2_D1_P | CSI3_D1_P | CSI4_D1_P | CSI6_D1_P | ||||||

| 11 | CSI0_D1_N | CSI1_D1_N | CSI2_D1_N | CSI3_D1_N | CSI4_D1_N | CSI6_D1_N | ||||||

| 12 | GND | GND | GND | GND | GND | GND | ||||||

| 13 | CSI0_D0_P | CSI1_D0_P | CSI2_D0_P | CSI3_D0_P | CSI4_D0_P | CSI6_D0_P | ||||||

| 14 | CSI0_D0_N | CSI1_D0_N | CSI2_D0_N | CSI3_D0_N | CSI4_D0_N | CSI6_D0_N | ||||||

| 15 | GND | GND | GND | GND | GND | GND | ||||||

| J13 | |||||||||||

| Pin NO. | NAME | Remarks | Pin NO. | NAME | Remarks | Pin NO. | NAME | Remarks | Pin NO. | NAME | Remarks |

| 1 | CSI0_D0_P | 31 | CSI2_D1_P | 61 | NC | 91 | NC | ||||

| 2 | CSI1_D0_P | 32 | CSI3_D1_P | 62 | NC | 92 | NC | ||||

| 3 | CSI0_D0_N | 33 | CSI2_D1_N | 63 | NC | 93 | NC | ||||

| 4 | CSI1_D0_N | 34 | CSI3_D1_N | 64 | NC | 94 | NC | ||||

| 5 | GND | 35 | GND | 65 | NC | 95 | NC | ||||

| 6 | GND | 36 | GND | 66 | NC | 96 | NC | ||||

| 7 | CSI0_CLK_P | 37 | CSI4_D0_P | 67 | NC | 97 | NC | ||||

| 8 | CSI1_CLK_P | 38 | CSI6_D0_P | 68 | NC | 98 | NC | ||||

| 9 | CSI0_CLK_N | 39 | CSI4_D0_N | 69 | GND | 99 | GND | ||||

| 10 | CSI1_CLK_N | 40 | CSI6_D0_N | 70 | GND | 100 | GND | ||||

| 11 | GND | 41 | GND | 71 | NC | 101 | NC | ||||

| 12 | GND | 42 | GND | 72 | NC | 102 | NC | ||||

| 13 | CSI0_D1_P | 43 | CSI4_CLK_P | 73 | NC | 103 | NC | ||||

| 14 | CSI1_D1_P | 44 | CSI6_CLK_P | 74 | NC | 104 | NC | ||||

| 15 | CSI0_D1_N | 45 | CSI4_CLK_N | 75 | CAM_I2C_SCL | 1.8V Level | 105 | NC | |||

| 16 | CSI1_D1_N | 46 | CSI6_CLK_N | 76 | NC | 106 | NC | ||||

| 17 | GND | 47 | GND | 77 | CAM_I2C_SDA | 1.8V Level | 107 | NC | |||

| 18 | GND | 48 | GND | 78 | NC | 108 | VDD_3V3_SLP | PWR | |||

| 19 | CSI2_D0_P | 49 | CSI4_D1_P | 79 | GND | 109 | NC | ||||

| 20 | CSI3_D0_P | 50 | CSI6_D1_P | 80 | GND | 110 | VDD_3V3_SLP | PWR | |||

| 21 | CSI2_D0_N | 51 | CSI4_D1_N | 81 | NC | 111 | NC | ||||

| 22 | CSI3_D0_N | 52 | CSI6_D1_N | 82 | NC | 112 | NC | ||||

| 23 | GND | 53 | GND | 83 | NC | 113 | NC | ||||

| 24 | GND | 54 | GND | 84 | NC | 114 | NC | ||||

| 25 | CSI2_CLK_P | 55 | NC | 85 | NC | 115 | GND | ||||

| 26 | CSI3_CLK_P | 56 | NC | 86 | NC | 116 | GND | ||||

| 27 | CSI2_CLK_N | 57 | NC | 87 | NC | 117 | NC | ||||

| 28 | CSI3_CLK_N | 58 | NC | 88 | NC | 118 | TX2 :VDD_5V0_IO_SYS AGX:VDD_3V3_IO_SYS | PWR | |||

| 29 | GND | 59 | NC | 89 | NC | 119 | NC | ||||

| 30 | GND | 60 | NC | 90 | NC | 120 | TX2 :VDD_5V0_IO_SYS AGX:VDD_3V3_IO_SYS | PWR | |||